## **TEST BENCH**

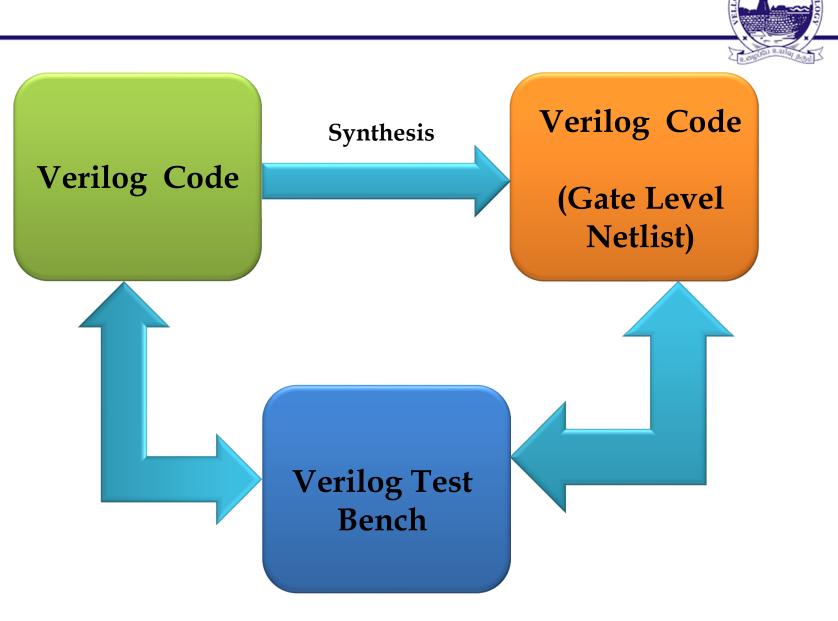

What is test bench?

- A Verilog procedural block which executes only once.

- Used for simulation.

- Test bench generates clock, reset, and the required test vectors

- Create a dummy template

- -Declare inputs to the module-under-test (MUT) as

- "reg", and the outputs as "wire"

- Instantiate the MUT.

- Initialization

- Assign some known values to the MUT inputs.

- Clock generation logic

- Various ways to do so.

- May include several simulator directives

- Like \$display, \$monitor, \$dumpfile, \$dumpvars,

\$finish.

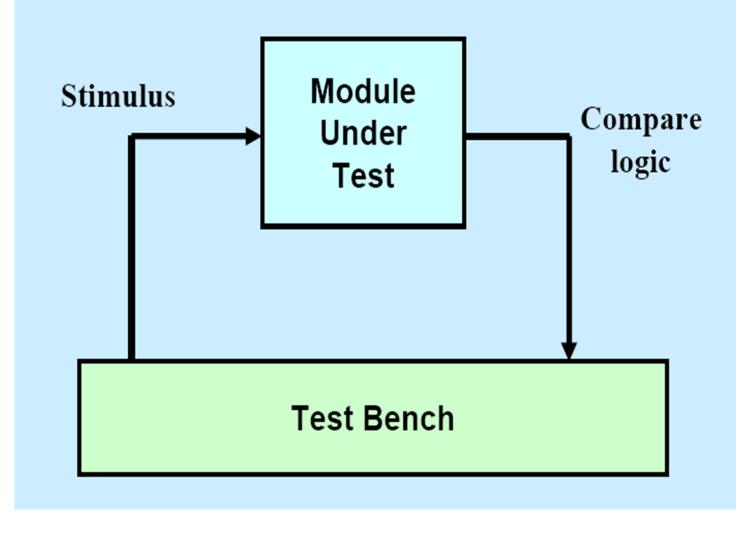

- •Once a design block is completed, it must be tested

- •A design block needs to be tested for its functionality by applying stimulus and checking results.

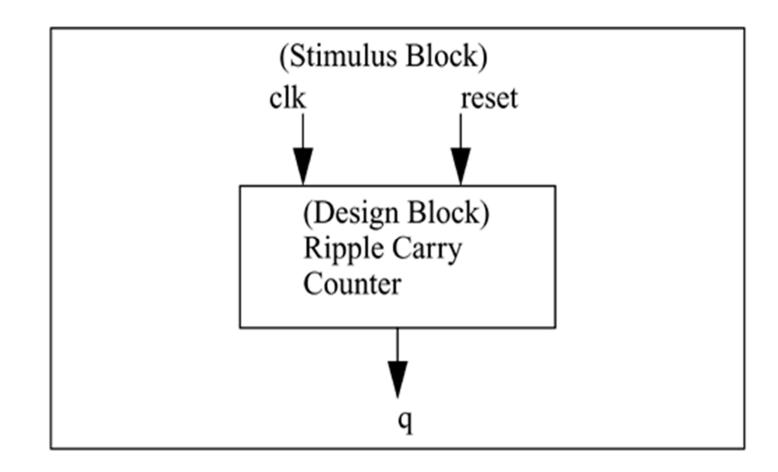

- For testing the design block, a stimulus block or test bench can be created in Verilog itself.

- In the test bench we provide some stimulus to the corresponding inputs of the design module.

## **Stimulus Block Instantiates Design Block**

## Example

module and\_gate (a,b,y);

input a,b;

output y;

assign y= a & b;

endmodule

module and\_test (); **reg** a,b; wire y; and\_gate a1(a,b,y); initial begin a=1'b0;b=1'b0; #100; a=1'b0; b=1'b1; #100; a=1'b1; b=1'b0; #100; a=1'b1; b=1'b1; end endmodule

## Example

module CC (a,b,c,d,y);

input a,b,c,d;

output y;

assign y = (d==0) ? (a & b & c) : (a ^ b ^ c); endmodule module CombinationalCircuit\_TB;

reg a,b,d,c;

wire y;

CC dut (.a(a),.b(b), .c(c),.d(d),.y(y));